# **GUNTETCO**

# Infinity Series H.100 MC3 Multi-chassis Interconnect & Conference Board

TECHNICAL MANUAL

Documentation Revision 1.1: July 31, 2003

Copyright © 2000, 2003 by American Tel-A-Systems, Inc. All rights reserved. 257M000C **NOTE:** This manual specifically refers to firmware version V02.1A. Some aspects of this manual relating to conferencing limits apply only to this and later versions. As this firmware version will will only run on boards of hardware revision 257A002F or later, this manual is not applicable to earlier boards. For details on earlier boards refer to manual 257M000A.

### Contents

| 1.0 | INTRO          | DUCTION 1-1                               |  |

|-----|----------------|-------------------------------------------|--|

|     | 1.1            | Features and Capacities 1-2               |  |

|     |                | 1.1.1 The H.100 Bus 1-2                   |  |

|     |                | 1.1.2 The MC3 Bus Interface               |  |

|     |                | 1.1.3 Conferencing 1-3                    |  |

|     |                | 1.1.4 DSP Functions 1-4                   |  |

|     |                | 1.1.5 Analog Audio Port 1-4               |  |

|     |                | 1.1.6 Clock Modes 1-5                     |  |

|     |                | 1.1.7 Message Passing 1-5                 |  |

|     |                | 1.1.8 Flash EAROM for Firmware 1-5        |  |

|     | 1.2            | How to Use This Manual 1-6                |  |

| 2.0 | Quici          | k Start                                   |  |

| 3.0 | Insta          | LLATION                                   |  |

|     | 3.1            | PCI Configuration                         |  |

|     | 3.2            | Jumpers & Headers 3-2                     |  |

|     | 3.3            | Connectors: P2, P5, P6 and J1 3-3         |  |

|     | 3.4            | Installation                              |  |

| 4.0 | INITIALIZATION |                                           |  |

|     | 4.1            | PCI Initialization                        |  |

|     | 4.2            | Initialization Commands 4-2               |  |

| 5.0 | Соми           | AUNICATING WITH THE PC                    |  |

|     | 5.1            | Command and Response Protocol 5-2         |  |

|     |                | 5.1.1 Sending Commands to the Board 5-2   |  |

|     |                | 5.1.2 Reading Messages From the Board 5-2 |  |

|     |                | 5.1.3 Reading Board Information 5-3       |  |

|     | 5.2            | Interrupts 5-3                            |  |

|     |                | 5.2.1 Interrupt Initialization            |  |

|     |                | 5.2.2 Step-by-Step Summary 5-4            |  |

|     |                |                                           |  |

|   | •• |   |

|---|----|---|

| • | u  | • |

| 5.0 | COMMUNICATING WITH THE PC (CONTINUED): |                                                          |  |

|-----|----------------------------------------|----------------------------------------------------------|--|

|     | 5.3                                    | Commands and Responses 5-5                               |  |

|     |                                        | 5.3.1 Characteristics of Command Strings 5-5             |  |

|     |                                        | 5.3.2 Command Parameters 5-5                             |  |

|     |                                        | 5.3.3 Commands to the H.100 MC3/Conference Board 5-6     |  |

|     |                                        | < Conference Commands 5-6                                |  |

|     |                                        | < MC3 Bus Commands 5-7                                   |  |

|     |                                        | < Analog Port Control 5-7                                |  |

|     |                                        | < MVIP Compatibility Commands                            |  |

|     |                                        | < Interrupt Control Commands                             |  |

|     |                                        | < Reset Commands 5-8                                     |  |

|     |                                        | < Setup Commands 5-8                                     |  |

|     |                                        | < Tone Plant Commands                                    |  |

|     |                                        | < Version Requests                                       |  |

|     |                                        | < Download Commands 5-10                                 |  |

|     |                                        | < Diagnostics 5-10                                       |  |

|     |                                        | 5.4.4 Responses from the H.100 MC3/Conference Board 5-10 |  |

|     |                                        | < Acknowledgments 5-10                                   |  |

|     |                                        | < Error Messages 5-10                                    |  |

|     |                                        | < Query Responses 5-11                                   |  |

|     |                                        | < DTMF Detection & Generation Messages 5-11              |  |

|     |                                        | < Diagnostic Responses 5-11                              |  |

| 6.0 | THE H.100 BUS, CLOCK MODES & MC3 BUS   |                                                          |  |

|     | 6.1                                    | The H.100 Bus                                            |  |

|     |                                        | 6.1.1 Legacy Bus Compatability 6-2                       |  |

|     | 6.2                                    | Clock Modes                                              |  |

|     |                                        | 6.2.1 Slave Mode 6-4                                     |  |

|     |                                        | 6.2.2 Primary Master Mode                                |  |

|     |                                        | 6.2.3 Secondary Master Mode 6-6                          |  |

|     |                                        | 6.2.4 Clock Fallback 6-6                                 |  |

|     |                                        | 6.2.5 Clock Errors                                       |  |

|     | 6.3                                    | The MC3 Bus                                              |  |

|     |                                        | 6.3.1 MC3 Ring Errors 6-8                                |  |

|     | 6.4                                    | MC3 Ring Configurations 6-9                              |  |

|     | 6.5                                    | Configuration Information 6-10                           |  |

### • *iii* •

| 7.0  | Using | G THE MC3 BUS                                |

|------|-------|----------------------------------------------|

|      | 7.1   | Initialization                               |

|      | 7.2   | Ring Switching Commands                      |

|      | 7.3   | Ring Errors                                  |

|      | 7.4   | Ring Redundancy & Fallback                   |

|      | 7.5   | Loopback Modes                               |

| 8.0  | CT B  | US BUS SWITCHING                             |

|      | 8.1   | The H.100 Switching Hardware                 |

|      | 8.2   | SCbus Compatability 8-1                      |

|      |       | 8.2.1 Timeslot Assignment 8-2                |

|      | 8.3   | MVIP Compatability 8-4                       |

|      |       | 8.3.1 MVIP Compatibility Commands 8-5        |

|      | 8.4   | The Analog Port 8-7                          |

| 9.0  | CONF  | erencing                                     |

|      | 9.1   | The Conferencing Hardware 9-1                |

|      |       | 9.1.1 Conference Handles 9-1                 |

|      |       | 9.1.2 Command Set 9-2                        |

|      |       | 9.1.3 Attenuation & Noise Threshold          |

|      |       | 9.1.4 DSP Facilities                         |

|      | 9.2   | Controlling Conferences                      |

|      | 9.3   | Changing the Attenuation and Noise Threshold |

|      | 9.4   | DTMF Detection                               |

|      | 9.5   | Tone Plant Facilities                        |

|      | 9.6   | Energy Detection                             |

|      | 9.7   | 2 kHz. Tone Generation and Detection         |

|      | 9.8   | Conferencing Examples                        |

| 10.0 | DIAG  | NOSTICS & ERROR MESSAGES 10-1                |

|      | 10.1  | Diagnostic Commands 10-1                     |

|      | 10.2  | Error Messages                               |

|      | 10.3  | QM Queries                                   |

#### • iv •

APPENDIXES:

| A. | Environmental Specifications  | A-1 |

|----|-------------------------------|-----|

| B. | Notes on H.100 MC3 Redundancy | B-1 |

### Infinity Series H.100 MC3 Multi-Chassis Interconnect & Conference Board Technical Manual

Copyright © American Tel-A-Systems, Inc., July 2003 Printed in U.S.A. All rights reserved.

This document and the information herein is proprietary to American Tel-A-Systems, Inc. It is provided and accepted in confidence only for use in the installation, operation, repair and maintenance of Amtelco equipment by the original owner. It also may be used for evaluation purposes if submitted with the prospect of sale of equipment.

This document is not transferable. No part of this document may be reproduced in whole or in part, by any means, including chemical, electronic, digital, xerographic, facsimile, recording, or other, without the express written permission of American Tel-A-Systems, Inc.

The following statement is in lieu of a trademark symbol with every occurrence of trademarked names: trademarked names are used in this document only in an editorial fashion, and to the benefit of the trademark owner with no intention of infringement of the trademark. "MVIP", "H-MVIP" and "MVIP-90" are registered trademarks of GO-MVIP. "SCSA" and "SCbus" are registered trademarks of the Dialogic Corportation. "CT bus" and "ECTF" are registered trademarks of the Enterprise Computer Telephony Forum

American Tel-A-System, Inc.

- 800-356-9148

- 4800 Curtin Drive McFarland, WI 53558 •

- 4145 North Service Road, Suite 200 Burlington, Ontario L7L 6A3

- 257M000C •

• vi •

#### FCC Part 15 Requirements

WARNING: This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instruction manual, may cause interference to radio communications. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

#### FCC Part 68 Registration

This equipment is registered with the FCC under Part 68 as a component device for use with any generic PC Type computer or compatible. In order for FCC registration of this product to be retained, all other products used in conjunction with this product to provide your telephony function must also be FCC Part 68 registered for use with these hosts. If any of these components are not registered, then you are required to seek FCC Part 68 registration of the assembled equipment prior to connection to the telephone network. Part 68 registration specifies that you are required to maintain the approval and as such become responsible for the following:

- any component device added to your equipment, whether it bears component registration or not, will require that a Part 68 compliance evaluation is done and possibly that you have testing performed and make a modification filing to the FCC before that new component can be used;

- any modification/update made by a manufacturer to any component device within your equipment, will require that a Part 68 compliance evaluation is done and possibly that you have testing performed and make a modification filing to the FCC before the new component can be used;

- if you continue to assemble additional quantities of this compound equipment, you are required to comply with the FCC's Continuing Compliance requirements.

The telephone company has the right to request the registration information.

The telephone company has the right to temporarily discontinue service. They are required to provide notification and advise of the right to file a complaint.

In case of trouble, you may be required to disconnect the board from the telephone lines until the problem is resolved.

The authorized repair center is:

American Tel-A-System, Inc. 800-356-9148 4800 Curtin Drive McFarland, WI 53558

There are no user serviceable components on the board. All repairs should be accomplished by returning the board to Amtelco with a description of the problem.

**WARNING:** This device contains Electrostatic Sensitive Devices. Proper care should be taken when handling this device to avoid damage from static discharges. • *viii* •

**Canadian Customers**

CP-01, Issue 8, Part 1 Section 14.1

**Notice:** "The industry Canada label identifies certified equipment. This certification means that the equipment meets certain telecommunications network protective, operational and safety requirements as prescribed in the appropriate Terminal Equipment Technical Requirements document(s). The Department does not guarantee the equipment will operate to the user's satisfaction.

Before installing this equipment, users should ensure that it is permissible to be connected to the facilities of the local telecommunications company. The equipment must also be installed using an acceptable method of connection. The customer should be aware that compliance with the above conditions may not prevent degradation of service in some situations.

Repairs of certified equipment should be coordinated by a representative designated by the supplier. Any repairs or alterations made by the user to this equipment, or equipment malfunctions, may give the telecommunications company cause to request the user to disconnect the equipment.

Users should ensure for their own protection that the electrical ground connections of the power utility, telephone lines and internal metallic water pipe system, ir present, are connected together. This precaution may be particularly important in rural areas.

**CAUTION:** Users should not attempt to make such connections themselves, but should contact the appropriate electric inspection authority, or electrician, as appropriate.

### **European Approvals**

### **CE** Approval

CE

#### **EN55022 EMC declaration**

This is a class B product. In a domestic environment, this product may cause radio interference in which case the user may be required to take adequate measures.

No changes or modifications to the MC3 Board are allowed without explicit written permission from American Tel-A-Systems, Inc., as these could void the end user's authority to operate the device.

• ix •

• x •

this page intentionally left blank

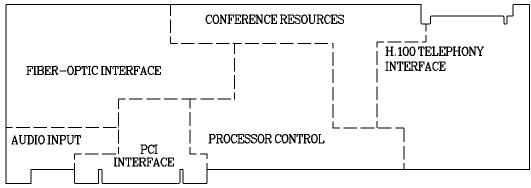

# **1.0 Introduction**

The Infinity Series H.100 MC3 Multi-chassis Interconnect & Conference Board is designed to provide a high capacity interconnect path between multiple computers using the H.100 bus to connect computer telephony boards within the chassis. This path is provided by fiber-optic links conforming to the MC3 standard and operating at the OC3 bit rate of 155 Mbps. Provisions are included for supporting dual counter rotating rings for redundancy or higher capacity.

In addition to the multi-chassis function, the board is equipped with enhanced conferencing facilities for up to 84 conferences with a total of 256 participants. For backwards compatibility with older revision boards there is a 128 party conference mode. Enhanced features include individual DTMF detection for each conference participant, a "clamping" function to prevent conferees from hearing DTMF tones generated by other conferees, and energy detection capabilities for conference inputs. A bidirectional analog port is also provided for such functions as music on hold and monitoring.

The H.100 bus was devised by the Enterprise Computer Telephony Forum (ECTF) to provide a single telecom bus for the entire industry. It is intended for add-in boards using the PCI form factor. A wide variety of boards are available from a number of different vendors. The MC3 bus is a chassis interconnect standard promulgated by the GO-MVIP standards body.

The board is equipped with a processor that can be used to control the lower level functions of the board. The host PC controls the board using messages passed through dual-ported RAM. The board shares a common message passing and control scheme with other Infinity Series H.100 boards. This scheme is also compatible with legacy XDS boards for the MVIP-90 bus and SCbus.

Figure 1: The H.100 MC3/Conference Board Functional Areas

### **1.1 Features and Capabilities**

This section presents an overview of the features and capabilities of the Infinity Series MC3 Multi-chassis Interconnect and Conferencing Board.

### 1.1.1 H.100 Bus

The H.100 bus is a digital bus for transporting PCM (Pulse Code Modulation) signals between telephony boards. It was created by the ECTF to provide a common bus structure for future development that would end the "bus wars" between the various legacy busses such as the SCbus and the MVIP bus.

PCM is a standard method of digitizing phone signals. It involves encoding each channel at an 8 kHz rate using eight bits. The signals from multiple channels are then combined into a frame. On the H.100 bus, each frame consists of 128 channels or timeslots. The bit rate of the H.100 bus is 8.192 MHZ. Thirty-two wires, also called streams, each carrying 128 timeslots, are combined to form the bus, and provide a total of 4096 timeslots. Two timeslots are required for a full conversation, one for each talker. For compatibility purposes with legacy busses, the first sixteen streams can also run at either 2.048 or 4.096 MHZ. with 32 or 64 timeslots respectively.

#### Introduction

In addition to the streams, a number of other signals necessary to maintain synchronization between all the boards in the system are carried on the bus. These signals provide the clocking and framing information. Redundant clocks are provided to aid in recovery if the primary clock should fail. For interoperation with the SCbus, MVIP bus, or H.MVIP bus a number of compatibility clock signals are also defined.

The H.100 bus consists of a 68 conductor ribbon cable that is used to interconnect the boards in the system. This cable connects to a header at the upper right hand edge on each board.

### 1.1.2 The MC3 Bus Interface

The MC3 bus was devised by GO-MVIP as a means of providing a large number of 64 kbps channels between PC chassis using the MVIP bus for intra-chassis connections. In the interest of minimizing cost and taking advantage of existing hardware, the physical interface uses the same architecture as that used by the SONET standard operating at the OC3 bit rate of 155 Mbps.

Each link consists of a full duplex fiber-optic cable that can support 2430 channels. Seven of these channels are dedicated to framing purposes. The MC3 standard arranges two of these fiber links in dual counter rotating rings. The two rings can be used to provide redundancy against ring or chassis failure or they can be used to double the capacity. Each node of the MC3 structure provides bypass, drop and insert capabilities for each of the 64 kbps channels.

The Infinity Series H.100 MC3/Conference Board provides up to 1024 connections in each direction between the MC3 and H.100 busses.

### **1.1.3 Conferencing**

In addition to support for the MC3 bus, the H.100 MC3/Conference Board also includes enhanced conferencing facilities. Up to 84 simultaneous conferences can be supported with a total of 256 participants. The transmit

and receive attenuation of each conferee can be controlled independently improving audio quality and making larger conferences practical. As a separate resource connected directly to the H.100 bus the conference facilities can connect to sources both within and external to the PC. When enabled, the conference facilities reduce the MC3 connectivity by 256 connections. For backwards compatibility with older revisions of this board, there is a 128 party conference mode. This mode will reduce the MC3 connectivity by 128.

### **1.1.4 DSP Functions**

The H.100 MC3/Conference Board is equipped with four DSP's associated with the conferencing facilities. A DTMF detector is available for each potential conferee. The DSPs also provide a "clamping" feature which when enabled will temporarily interrupt a connection when a DTMF digit is detected. This can be used to prevent other members of a conference from hearing a DTMF tone generated by a conferee. There is also an energy detection capability that can be used to detect the loudest talkers in a conference.

For systems that lack tone plant facilities, the DSPs can be set to provide up to 32 DTMF generators and either North American or European standard call progress tones. Doing so reduces the number of conferees available by 32.

In addition to DTMF tone detection, the DSPs can be used to generate and detect 2 kHz. tones which are used for performing continuity checks for Signaling System 7.

### 1.1.5 Analog Audio Port

The H.100 MC3/Conference Board also provides a bidirectional analog port that can be used for such purposes as providing music on hold or monitoring.

### 1.1.6 Clock Modes

The H.100 MC3/Conference Board can operate in a variety of clock modes. Modes are available so that the master clock can either be derived from the H.100 bus, one of the MC3 rings, or be generated internally on the MC3/Conference Board.

### **1.1.7 Message Passing**

The board occupies 8K of memory space on the host PC. This 8K may reside anywhere within the PC's address space. As a PCI board, the address and interrupt of the board is assigned at boot time. The message passing scheme used by the Infinity Series H.100 MC3/Conference Board is identical to that of the other Infinity Series H.100 boards, allowing for the easy combination of a variety of Infinity Series H.100 boards in a single system.

The message passing scheme and message syntax of Infinity Series H.100 boards is similar to that of the older XDS series of MVIP and SCbus boards. At the driver and API level, support is provided for both series of boards so that the H.100 boards may interoperate with legacy boards using a common interface.

### **1.1.8 Flash EAROM for Firmware**

The firmware for both the main processor and for the DSP's is contained in Flash EAROM. This allows for easy upgrades of the firmware on the board in the field without requiring time consuming downloads every time a system boots. Once reprogrammed, the new firmware is retained even when the power is removed. The original, factory programmed firmware is also retained on board and can be accessed by installing a jumper.

### 1.2 How to Use This Manual

The first five sections in this manual are organized in the order you should read and use them to get started with your H.100 MC3/Conference Board. We recommend that you begin with these three steps.

- 1. Follow the instructions in section 2.0 (Quick Start) and 3.0 (Installation). These sections will tell you if your board is operating correctly within your system. You don't need to be familiar with the board's command set to complete this step.

- 2. Read section 4.0 (Initialization) to initialize the board within your system. Your application must perform these initialization procedures whenever you power-up your PC in order for the board to communicate with the PC.

- 3. Read section 5.0 (Communications with the PC) for an overview of how to communicate with the H.100 MC3/Conference Board. Section 5.0 includes a summary of the commands for constructing your application and details concerning system interrupts.

Before you can actually build your application, read section 6.0 (The H.100 bus, MC3 Bus and Clock Modes), 7.0 (Using the MC3 bus), 8.0 (H.100 Bus Switching) and 9.0 (Conferencing). These sections explain, with practical examples, how the H.100 MC3/Conference Board operates and how to use the command set to achieve the desired results.

Section 10.0 explains diagnostic and error messages that may occur.

The Appendices contains specifications and information that will be helpful installing and using your H.100 MC3/Conference Board.

# 2.0 Quick Start

This section describes the first steps you should perform to determine if your Infinity Series MC3 Multi-Chassis Interconnect & Conference Board is communicating correctly with your PC system. You can perform this quick check without securing the board to the PC chassis or connecting any cables.

The exact procedure will vary depending on which operating system you are running. For each operating systems, drivers are required to interface to the boards. The drivers supplied by Amtelco have tests built into them to verify communications with the boards. These drivers also come supplied with utility programs that allow the developer to test communications with the board. Please consult the appropriate documentation for the driver and operating system you are using.

#### **Quick Start Procedure**

- 1. Make sure the PC power is off, then insert the board into a PCI slot.

- 2. Turn on your PC.

- 3. If the Amtelco driver is not already installed, install it now, following the instructions supplied with the driver.

- 4. Most Amtelco drivers will display a list of boards that are installed (see the documentation for the particular driver that you are using). If the H.100 MC3/Conference board is listed, skip to step 6.

- 5. If the board is not listed, there may be a problem with the board not being seated correctly in the motherboard. There may also be a problem with a memory or interrupt conflict. Power down the PC and check that the board is properly seated in the connector and repeat steps 1-4. If this does not remedy the problem, try removing any other computer telephony boards in the system. If your PC is unable to find the board, consult the number at the end of this section.

- 6. Run the program "xdsutil" supplied with the driver. Send the message "IN" to the H.100 MC3/Conference board. The board should respond with the message "IA".

- 7. Send the message "VC" to the board. Verify that the Receive Message reads: VCxxxxvvvP03A (where xxxxvvvv is a variable indicating the firmware version).

- 8. If the Communications screen shows the correct command responses, your H.100 MC3/Conference Board is communicating with the PC. You may now power down the computer and attach the necessary cables (see section 3.4)

For technical assistance, call Amtelco at 1-608-838-4194 ext.168.

## 3.0 Installation

This section describes how to install your Infinity Series H.100 MC3 Multi-Chassis Interconnect and Conference Board into your PC and how to set the switches, jumpers, and connectors. Before you begin the installation procedure, be sure to test the board as described in section 2.0 (Quick Start).

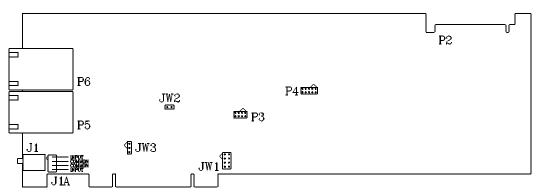

Figure 2: Location of Jumpers, Headers, and Connectors

### 3.1 PCI Configuration

As Infinity Series boards conform to the PCI standards, there are no switches to set to configure the H.100 MC3/Conference Board's memory address, I/O addresses, or interrupt. The PC's bios will automatically configure the board at boot time to avoid conflicts with other boards in the system.

### 3.2 Jumpers & Headers

The following is a complete list of all jumpers for the H.100 MC3/Conference Board:

- **JW1-1** Firmware Select. If firmware has been downloaded to the board, this jumper selects whether the downloaded firmware or the factory default firmware is used. When this jumper is installed, the factory default firmware is executed whenever the board is reset. When the jumper is not installed, the downloaded firmware will be executed after a reset if it is present. If no downloaded firmware is present, the factory default firmware is executed after reset.

- **JW1-2** DSP Firmware Select. Two separate firmware programs are included in the EAROM, one for the board processor and one for the DSP. If JW1-2 is installed and downloaded DSP firmware is present, the factory DSP firmware is executed after reset. Otherwise, the downloaded firmware is executed if present. See JW1-1

- **JW1-3** Undefined, reserved for future use.

- **JW1-4** Undefined, reserved for future use..

- **JW2, JW3** These jumpers are used for factory testing and should not have jumpers installed.

- P3 Diagnostic port. Never install jumpers here.

- P4 This header is used for programming internal logic and should never be jumpered.

### 3.3 Connectors: P2, P5, P6 and J1

- P2 H.100 bus. The H.100 bus connector (P2) is a standard H.100 bus header. Use an H.100 bus ribbon cable to connect the H.100 MC3/Conference Board to other H.100 boards within the same PC chassis.

- **P5** Ring 0 RCV, Ring 1 XMT. This is one of the two fiber optic transceivers for the MC3 bus. In a normal counter rotating ring connection, the fibers from this transceiver are connected to **P6** in the next chassis in the ring. This connector is keyed to insure proper insertion.

- P6 Ring 1 RCV, Ring 0 XMT. This is one of the two fiber optic transceivers for the MC3 bus. In a normal counter rotating ring connection, the fibers from this transceiver are connected to P5 in the previous chassis in the ring. This connector is keyed to insure proper insertion.

- J1 Analog port. This port can be used to connect a music source or other device analog port for music on hold. The connector is a standard 1/8" headphone jack. The music source should be at standard line levels.

- J1A Analog input. This header is connected in parallel with J1. It will connect with the audio output of a PC CD-ROM drive.

#### • 3-4 •

### 3.4 Installation

To install the H.100 MC3/Conference Board in your system:

- 1. Follow the quick check procedures described in section 2.0 to verify the operation of the board.

- 2. If the quick check is successful, turn off the PC power and remove the board from the chassis.

- 3. Install any necessary board jumpers. See section 3.2 for jumper configurations.

- 4. Insert the board into the chassis. Seat it properly in a PCI slot in the PC chassis and tighten the screw in the back of the board to secure it.

- 5. Connect the H.100 bus cable to P2.

- 6. Connect the fiber optic cables to P5 and P6. See section 6.4 for details on the various ring configurations.

- 7. If the analog port is to be used, connect the music source or other compatible device.

- 8. Power up the computer.

# 4.0 Initialization

This section describes the procedures necessary to initialize the system and enable the PC to communicate with the Infinity Series H.100 MC3 Multi-Chassis Interconnect and Conference Board. XDS drivers will implement some of these procedures.

### 4.1 PCI Initialization

The system BIOS is responsible for recognizing PCI boards and mapping them into the I/O and memory spaces as required. It is also responsible for assigning interrupts to the board. This is done through a set of on board registers which contain information specifying the memory, I/O, and interrupt needs of the board. A set of BIOS functions exist for accessing this information. A detailed description of these functions can be found in the *PCI BIOS Specification* published by the PCI SIG, the PCI Special Interest Group.

Normally, the drivers supplied by Amtelco will take care of the process of finding Infinity Series boards and establishing communications. The information in the rest of this subsection is for background only.

The configuration registers of every PCI board contain a vendor ID and device ID code. These codes are unique to each board vendor. All Infinity Series H.100 boards have the same vendor and device IDs. The vendor ID is 14E3h and the device ID is 0001h. A BIOS function exists that will find each instance of a particular vendor and device ID, and which returns with a bus and device number. The bus and device number is then used in functions to read the configuration registers.

The configuration registers contain information on the base address of the memory and I/O assigned to the board by the BIOS. A PCI board may

have up to six different base addresses. On Infinity Series H.100 boards, the first two base addresses are used by the PCI bus interface logic. The third base address which is contained in registers 18-1Bh contains the memory location of the dual-ported memory that is used to pass messages. The interrupt information is contained in register 3Ch. The information in these configuration registers can be used by a driver to address the board.

### 4.2 Initialization Commands

The H.100 MC3/Conference Board is initialized by sending a sequence of command messages to the board. The process of sending messages is described in detail in Section 5.0, but normally it is accomplished either with a low-level driver XMT command or the API function **xds\_msg\_send.** Response messages are read using the low-level driver RCV command or the API function **xds\_message\_receive**.

To enable communications with the H.100 MC3/Conference Board, an **IN** command message should be sent to the board. The board will respond with an **IA** message.

The board may be reset using the command message **RA**. The board will respond with an **RA** message.

Your application can now configure the H.100 MC3/Conference Board using these commands

- Command Purpose

- **SCmsabb(c)** Sets the clock mode for the board. The parameter m is the clock-mode. The parameters s is the clock submode. The parameters a, bb, and c are used to specify additional clock control information such as compatibility modes, clock rates, local network, and CT\_NETREF settings. The default mode on power-up or restart is mode 0. See section 6.0 of this manual for details of clock mode arguments.

- SBabcd This command is used to define the clock rate for the lower 16 streams for compatibility with the SCbus or MVIP bus. The parameters a, b, c, d are used to set the rate for streams 0-3, 4-7, 8-11, and 12-15 respectively. The default is 8.192 MHZ. The possible settings are:

0 2.048 MHZ., 32 timeslots per stream 1 4.096 MHZ., 64 timeslots per stream 2 8.192 MHZ., 128 timeslots per stream

- SEx Sets the encoding mode for the board. The parameter x can be M for Mu-Law as used in North America and Japan, A for A-Law as used in Europe and Asia, or L for linear encoding. The default value is for Mu-Law.

- **SKa(2)** This command is used to enable or disable conferencing. If the parameter a is D, conferencing will be disabled, if the parameter a is E, conferencing with 128 conferees will be enabled, if the optional "2" is added, conferencing will be enabled with 256 possible conferees. When conferencing is enabled, the maximum number of connections between the MC3 and H.100 bus is reduced from 1024 to 896 or 768 depending on which mode is enabled.

- **SMx** Selects the ring mode. The parameter x is used to choose between the extended mode where both rings are available and the redundant modes where one of the rings acts as the primary ring and the other as a backup. The choices for x are:

- 0 extended mode, 4846 timeslots

- 1 redundant mode, primary ring is 0, 2423 timeslots

- 2 redundant mode, primary ring is 1, 2423 timeslots

| • 4-4 • | Initialization |

|---------|----------------|

|         |                |

- **SPstt** When operating in SCbus compatibility mode, it may be desirable to restrict the number of timeslots that the board can use to transmit to the SCbus. This command restricts the total number of SCbus timeslots to s \* 64 + tt, where s and tt are in hexadecimal. This command is used in conjunction with the **SX** command and should only be used when operating in the SCbus mode.

- **SRx** Selects ring failure mode. If the board is to be operated with only a single ring due to a failure or configuration choice, this command is used to set the appropriate hardware. The choices for x are:

- 0 Both rings are operational

- 1 Ring 0 failure

- 2 Ring 1 failure

- 3 Both rings failed

**STab** Controls termination. Parameters a and b control termination for the H.100 and MVIP bus respectively. When set the E, termination is enable and when set to D, termination is disabled. Boards on the end of the H.100 cable should have termination enabled. When operating in MVIP compatibility mode, the MVIP termination should be enabled when the following condition exists:

For systems with five or fewer MVIP Bus connections and less than 90 pF load on the clock lines, it is adequate to place the circuit board that is the master clock source at one end of the cable and provide termination on the circuit board which is physically at the other end of the cable.

On systems with more than five MVIP connections or more than 90 pF load on the clock lines, both ends of the

cable should be electrically terminated with the 1000 Ohm/ 1000 pF termination. No other boards should terminate these lines.

**SXstt** This command is used to set the base timeslot on the SCbus when reserving timeslots to transmit on. The parameters s and tt are hexadecimal numbers setting the lowest timeslot of the block of timeslots reserved for the board. The number of timeslots reserved is defined by the **SP** command. This command should only be used when operating in the SCbus mode.

• 4-6 •

#### Initialization

This page left intentionally blank

# 5.0 Communicating with the PC

This section describes how the PC communicates with the Infinity Series H.100 MC3 Multi-chassis Interconnect and Conference Board. It includes the definitions for the H.100 MC3/Conference Board commands and responses along with a description of the mailboxes used for messaging.

The board is controlled by the host PC through a system of two mailboxes. The messages consist of short NUL-terminated ASCII strings, which are easy for the host software to compose and parse. The board is capable of buffering up to eight messages in either direction and can drive an interrupt line when it has a message for the host. Messages may not exceed 32 characters.

There are two mailboxes, one for messages to the board and one for messages from the board, and two flags associated with them. A 00h in a flag byte indicates the mailbox is free, a non-zero value indicates that the mailbox is occupied. The mailboxes and their flags are contained in an 8K block of dual-ported memory at the following offsets:

| receive mailbox  | 1F80h |

|------------------|-------|

| transmit mailbox | 1FC0h |

| transmit flag    | 1FFCh |

| receive flag     | 1FFEh |

The board's base address is determined by reading PCI Configuration Space offset 18h. The 32-bit value at this location is the base address for the dual-ported memory on the board.

To send a message, the message is placed in the mailbox and the flag is set to 01h. To read a message, the message is removed from the mailbox and the flag is cleared to 00h. This will clear the interrupt hardware.

### 5.1 Command and Response Protocol

This section describes the necessary step-by-step procedures for the PC to send a command to the board and to remove a response from the board.

### **5.1.1** Sending Commands to the Board

The basic steps to sending a command to the H.100 MC3/Conference Board are:

- 1. Build a command. Broadly speaking, a command is a string of ASCII characters with a null (00h) termination character.

- 2. Check the transmit flag. If the flag is 0, continue with the next step to put the command in memory. If the flag is not 0, wait until the flag is 0.

- 3. Insert the command in transmit mailbox memory beginning at the address of the transmit mailbox.

- 4. Write 01h to the transmit flag. This notifies the board that a message is waiting.

### 5.1.2 Reading Messages From the Board

- 1. Check the receive flag. If the flag is 0, there is no message. If it is non-zero, a message is waiting. Continue with the next step to read the message.

- 2. Remove the message from memory, starting at the address of the receive mailbox. The message is a NUL-terminated ASCII string.

- 3. Write 0h to the receive flag.

#### 5.1.3 Reading Board Information

A range of board information is included in memory so that it can be checked without sending a message:

| Type of Information          | Offset Address |

|------------------------------|----------------|

| Board ID                     | 1F00-1F03      |

| Firmware Version             | 1F04-1F07      |

| Number of transmit timeslots | 1F10-1F11      |

| Base timeslot                | 1F12-1F13      |

| Base timeslot of conferences | 1F14-1F15      |

| Base timeslot of analog port | 1F16-1F17      |

| Clock mode settings          | 1F18-1F1B      |

| Board configuration          | 1F1C-1F1E      |

| Clock status bits            | 1F1F           |

Note: The number of reserved transmit timeslots, and base timeslots are used only in the SCbus compatibility mode when reserving transmit timeslots.

The board stores its identity upon power up or a hardware restart. The phrase **Restart PCI MC3 (C) Amtelco 1999** appears in the receive mailbox. The receive flag is not set and no interrupt is generated.

### 5.2 Interrupts

The H.100 MC3/Conferencing Board can generate an interrupt to the PC indicating that a message is available. The interrupt for PCI boards is assigned by the BIOS or Operating System at boot time. The assignment is dependent on which PCI slot the board is in. The interrupt line is usually shared by more than one device. If multiple Infinity Series boards are installed they may or may not all share the same interrupt line.

In order for an Infinity Series board to send interrupts to the PC, the PCI Interface circuit on the board must be programmed to enable interrupts. This is accomplished by setting bits 0 and 3 in the board's Interrupt

Control/Status Register. This is a byte-wide register located at an offset of 69h from PCI Base Address 0. PCI Base Address 0 is contained in PCI Configuration Space register 10h. The Base address is a 32-bit value and is mapped into memory.

When an Infinity Series board sends a message, it generates a local interrupt to the PCI Interface circuit on the board. If the PCI Interface circuit has been programmed to generate interrupts to the PC, the local interrupt is passed through to the PC. When the PC receives an interrupt, its Interrupt Service Routine (ISR) should check the Infinity board's receive flag to see if a message is pending (i.e. the receive flag is non-zero). It should then process the message for the board and write a 0 to the board's receive flag.

### 5.2.1 Interrupt Initialization

- 1. Clear the board's receive flag.

- 2. Read the PCI Base Address 0 from PCI Configuration Space offset 10h (this must be a 32-bit access).

- 3. Set bits 0 and 3 of PCI Base Address 0 + 69h. Do not modify any other bits in this register. This register is a byte-wide memory mapped register.

### 5.2.2 Step-by-Step Interrupt Processing Summary

- 1. Check to see if the receive flag is non-zero.

- 2. Remove the message from the receive mailbox.

- 3. Write 0h to the receive flag.

- 4. Re-enable the interrupt controller on the PC.

The H.100 MC3/Conference Board

• 5-4 •

### **5.3** Commands and Responses

This section gives a general overview of the H.100 MC3/Conference Board commands and responses. The commands are grouped by function and then listed in alphabetical order by two-letter command. Refer to sections 7.0 through 10.0 for examples and explanations of how to use these commands.

### 5.3.1 Characteristics of Command Strings

- < All commands consist of null (00h) terminated ASCII strings.

- < There are no spaces or other delimiters between parameters in the commands.

- < All letters in command strings must be UPPERCASE unless otherwise noted.

- Lowercase monospaced letters (such as xx) in the following command references represent parameters within commands. Each letter represents one ASCII digit.

- < Numeric parameters are always hexadecimal numbers.

### **5.3.2 Command Parameters**

The following table documents the common parameters for many of the commands listed in the next sections. Other less common parameters are defined with individual commands.

| <b>Common Command Parameters</b> |                                                       |                         |

|----------------------------------|-------------------------------------------------------|-------------------------|

| Parameter                        | Definition                                            | Values                  |

| hh                               | Conference handle                                     | 01-54h                  |

| CC                               | Conference Control Address                            | 00-FFh                  |

| pp                               | Output pattern value                                  | 00-FFh                  |

| iiii                             | 1st & 2nd i, H.100 receive stream                     | 00-1Fh                  |

|                                  | 2nd & 3rd i, H.100 receive timeslot                   | 00-7Fh                  |

| 0000                             | 1st & 2nd o, H.100 transmit stream                    | 00-1Fh                  |

|                                  | 3rd & 4th o, H.100 transmit timeslot                  | 00-7Fh                  |

| уууу                             | 1st & 2nd y, MC3 transmit stream                      | 00-4Bh                  |

|                                  | 3rd & 4th y, MC3 transmit timeslot                    | 00-3Fh                  |

| ZZZZ                             | 1st & 2nd z, MC3 receive stream                       | 00-4Bh                  |

|                                  | 3rd & 4th z, MC3 receive timeslot                     | 00-3Fh                  |

| bsstt                            | MVIP terminus, b - bus,<br>ss - stream, tt - timeslot | C, H, L, X<br>0000-4B7F |

### 5.3.3 Commands to the H.100 MC3/Conference Board

Note that sections 7.0-9.0 provide supplemental information and examples for the commands and messages documented here.

#### **Conference Commands**

| CAhhooooiiiian | Conference H.100 timeslot iiii, output on timeslot    |

|----------------|-------------------------------------------------------|

|                | 0000, conference hh, attenuation a, noise threshold n |

| <b>CD0000</b>  | Disable output to H.100 timeslot oooo                 |

| CEiiii(cc)     | Enable DTMF detection on conferenced timeslot iiii,   |

|                | cc = clamping time .02 sec increments                 |

| CEiiiiD        | Disable DTMF detection on conferenced timeslot iiii   |

| CIhhiiiian | Add H.100 input timeslot iiii to conference hh attenuation a, noise threshold n |

|------------|---------------------------------------------------------------------------------|

| CLiiii     | Enable 2 kHz. tone detection on H.100 timeslot iiii                             |

| CLiiiiD    | Disable 2 kHz. tone detection on H.100 timeslot iiii                            |

| CMhhoooo   | Monitor conference hh on H.100 timeslot oooo                                    |

| СТооооЕ    | Enable 2 kHz. tone on H.100 timeslot oooo                                       |

| СТооооД    | Disable 2 kHz. tone on H.100 timeslot oooo                                      |

| CUhh       | Dissolve conference handle hh                                                   |

| CXhhiiii   | Remove H.100 timeslot iiii as an input to conference                            |

|            | hh                                                                              |

#### **MC3 Bus Commands**

| XCooooiiiiyyyyzz       | zz Connect H.100 timeslot iiii to MC3 transmit<br>timeslot yyyy and MC3 receive timeslot zzzz to<br>H.100 timeslot 0000 |

|------------------------|-------------------------------------------------------------------------------------------------------------------------|

| XDI0000                | Disable output to H.100 timeslot oooo from MC3 bus                                                                      |

| ХДОуууу                | Disable output to MC3 timeslot yyyy                                                                                     |

| XLI0000zzzz            | One-way audio from MC3 timeslot zzzz to H.100 timeslot oooo                                                             |

| XLOyyyyiiii            | One-way audio from H.100 timeslot iiii to MC3 timeslot yyyy                                                             |

| ХРІоооорр<br>ХРОуууурр | Output pattern pp on H.100 timeslot oooo<br>Output pattern pp on MC3 timeslot yyyy                                      |

# Analog Port Control (Music on Hold)

| Disable Music on Hold transmit                            |

|-----------------------------------------------------------|

| Enable Music on Hold output to H.100 timeslot oooo        |

| Set transmit attenuation to tt and receive attenuation to |

| rr in .1 dB steps                                         |

| Enable analog input from H.100 timeslot iiii              |

| Disable analog input                                      |

|                                                           |

#### **MVIP** Compatibility Commands

| The second se |                                                    |

|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| MAm                                                                                                             | Audio port control mode                            |

|                                                                                                                 | m = D - disabled, $m = E$ - enabled                |

| MDccmdd                                                                                                         | DTMF detection control, cc - CCA,                  |

|                                                                                                                 | m = D - disabled, $m = E$ - enabled, dd - duration |

| MKhhccman                                                                                                       | Conference control, hh - conference handle,        |

|                                                                                                                 | cc - CCA, $m = D$ - disabled, $m = E$ - enabled    |

|                                                                                                                 | a - attenuation, n - noise threshold               |

| MObssttD                                                                                                        | Set_output disable mode, bsstt - output terminus   |

| MObssttEbsstt                                                                                                   | Set_output enable mode, bsstt - output terminus,   |

|                                                                                                                 | bsstt - input terminus                             |

| MObssttPpp                                                                                                      | Set_output pattern mode, bsstt - output terminus,  |

|                                                                                                                 | pp - pattern value                                 |

| MTD                                                                                                             | Disable output to the CT Bus (tristate)            |

| MTE                                                                                                             | Enable output to the CT Bus                        |

#### **Interrupt Control Commands**

| IF | Disable transmit interrupts and messages |

|----|------------------------------------------|

| IN | Enable transmit interrupts and messages  |

#### **Reset Commands**

| RA | Reset All   |

|----|-------------|

| RD | Reset DSP's |

# **Setup Commands**

| SAhhan     | Set conference with handle hh to attenuation and noise |

|------------|--------------------------------------------------------|

|            | threshold n                                            |

| SBabcd     | Set bit rate for streams 0-3, 4-7, 8-11, and 12-15     |

|            | 0 - 2.048 MHZ.                                         |

|            | 1 - 4.096 MHZ.                                         |

|            | 2 - 8.192 MHZ.                                         |

| SCmsabb(c) | Set clock mode m submode s, arguments a, bb, & c       |

| SDm        | Set energy detection mode,                             |

|            | m = D - disabled, $m = E$ - enabled                    |

| SEm        | Set encoding mode, m = M - mu-Law, A - A-Law, L -      |

|            | linear encoding                                        |

| SKD<br>SKE<br>SKE2<br>SLx<br>SMx | Disable Conferencing<br>Enable Conferencing with 128 conference ports<br>Enable Conferencing with 256 conference ports<br>Set Loopback Mode $x = 0$ -F, $0 = no$ loopback<br>bit 0 - TLBB, 1 - FLBB, 2 - TLBA, 3 - FLBA<br>Set Ring Mode, $x = 0$ extended mode, both rings<br>available<br>1 - Redundant rings, Ring 0 primary ring |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  | 2 - Redundant rings, Ring 1 primary ring                                                                                                                                                                                                                                                                                             |

| SPstt                            | Set maximum number of transmit timeslots to stt                                                                                                                                                                                                                                                                                      |

| SRx                              | Select Ring Failure bits, $x = 0$ , no failure, $x = 1$ ring 0,                                                                                                                                                                                                                                                                      |

|                                  | x = 2 ring 1, $x = 3$ both rings                                                                                                                                                                                                                                                                                                     |

| STab                             | Set bus termination, $a = H.100$ bus, $b = MVIP$ bus                                                                                                                                                                                                                                                                                 |

| SXstt                            | Set base SCbus transmit timeslot to stt                                                                                                                                                                                                                                                                                              |

| Tone Plant Comm                  | ands                                                                                                                                                                                                                                                                                                                                 |

| ТА                               | Set call progress generators to North American tones                                                                                                                                                                                                                                                                                 |

| TDsstt                           | Disables tone plant output to stream ss, timeslot tt                                                                                                                                                                                                                                                                                 |

| TE                               | Set call progress generators to ETSI (European) tones                                                                                                                                                                                                                                                                                |

| TGsstt(d)                        | Generate tones string (d) on stream ss, timeslot tt                                                                                                                                                                                                                                                                                  |

| TPssttx                          | Sets call progress generator x to output on stream ss, timeslot tt                                                                                                                                                                                                                                                                   |

| TSm                              | Set tone plant mode m                                                                                                                                                                                                                                                                                                                |

|                                  | 0 - generators disabled                                                                                                                                                                                                                                                                                                              |

|                                  | 1 - 32 DTMF generators enabled                                                                                                                                                                                                                                                                                                       |

|                                  | 2 - 8 call progress generators enabled                                                                                                                                                                                                                                                                                               |

|                                  | 3 - 24 DTMF and call progress generators ena.                                                                                                                                                                                                                                                                                        |

| Version Requests                 |                                                                                                                                                                                                                                                                                                                                      |

| VA                               | Checksum of alternate segment request                                                                                                                                                                                                                                                                                                |

| VC                               | Version request                                                                                                                                                                                                                                                                                                                      |

| VD                               | DSP version request                                                                                                                                                                                                                                                                                                                  |

|                                  |                                                                                                                                                                                                                                                                                                                                      |

• 5-10 •

#### **Download Commands**

|             | lands                                               |

|-------------|-----------------------------------------------------|

| @xxxx       | Download 1K block to address xxxx                   |

| @Es         | Erase segment s                                     |

| GA          | Jump to Alternate Program                           |

| GM          | Jump to Main Program                                |

| @Ws         | Write from RAM to segment s                         |

| Diagnostics |                                                     |

| QC          | Query Clock Mode information                        |

| QHcrrrr     | Query CT812, $c = CT812$ , $rrrr = register$        |

| QMRx0zzz    | Query MC3 Receive, $x = MT90840$ , $zzz = internal$ |

|             | stream & timeslot                                   |

| QMTxyyyy    | Query MC3 Transmit, $x = MT90840$ , $yyyy = MC3$    |

|             | stream & timeslot                                   |

| QObsstt     | Query Output for terminus bsstt                     |

| QPd(cmnd)   | Send command to DSP d                               |

| QS          | Query MC3 bus status                                |

| QXxxx       | Query SCbus transmit timeslot for port xxx          |

# 5.4.4 Responses from the H.100 MC3/Conferencing Board

# Acknowledgments

| A(msg) | Verify set response to a message |

|--------|----------------------------------|

| IA     | Interrupt On acknowledge         |

| RA     | Reset all acknowledge            |

| <b>Error Messages</b> |                                                     |

|-----------------------|-----------------------------------------------------|

| ECxx                  | Clock error bits xx                                 |

| EFr                   | Ring r failure                                      |

| EG01                  | Conflict while enabling the 2 kHz. generator        |

| EKhhxx                | Conference error for conference handle hh, error xx |

|                       | 01 - illegal handle                                 |

|                       | 02 - no free conference inputs                      |

|                       | 03 - not an input to conference                     |

| EPoooo                | Path error for H.100 output timeslot xxx            |

| ERr                   | Ring r restored                                     |

| ESrxx                 | Ring r status error, status xx                      |

| Query Responses                              |                                                         |  |

|----------------------------------------------|---------------------------------------------------------|--|

| QCmsabrrttkkrsmxsy Reply to Query Clock Mode |                                                         |  |

|                                              | m - mode, s - submode, a, b - arguments                 |  |

|                                              | rr - stream rate byte, tt, kk - enable flags            |  |

|                                              | rs - reset byte, mx - mux byte, sy - SYN-155 byte       |  |

|                                              | Reply to CT812 query, dddddd is register data           |  |

| QMRx0zzzhhlldd                               | Reply to Query MC3 Receive,                             |  |

|                                              | hh = receive path connection memory high                |  |

|                                              | ll = receive path connection memory low                 |  |

|                                              | dd = transmit path data memory                          |  |

| QMTxyyyyhhlldd Reply to Query MC3 Transmit   |                                                         |  |

|                                              | hh = transmit path connection memory high               |  |

|                                              | ll = transmit path connection memory low                |  |

|                                              | dd = receive path data memory                           |  |

| QObssttm(bsstt)                              | Query_output reply, bsstt - output terminus, m - mode   |  |

|                                              | (bsstt) input terminus                                  |  |

| <b>QPd(string)</b>                           | Response from DSP d                                     |  |

| QSsstt                                       | MC3 bus status ss for ring 0, tt for ring 1             |  |

| QXxxxstt                                     | SCbus transmit timeslot for port xxx                    |  |

| QXxxxZ                                       | No SCbus transmit timeslot set for port xxx             |  |

| DTMF Detection & Generation Messages         |                                                         |  |

| STiiiit                                      | DTMF tone t detected on H.100 stream & timeslot iiii    |  |

| STX0cct                                      | DTMF tone t detected on CCA cc                          |  |

| TEsstt                                       | The tone string on stream ss, timeslot tt has completed |  |

| Diagnostic Responses                         |                                                         |  |

| VAcccc                                       | Alternate segment checksum, cccc - checksum             |  |

| VAcccc         | Alternate segment checksum, cccc - checksum |  |  |

|----------------|---------------------------------------------|--|--|

| VCccccvvvviiii | Version request response, cccc - checksum   |  |  |

|                | vvvv - version, iii - board identifier      |  |  |

|                | PO3A - PCI MC3 board, board revision A      |  |  |

| VDxxxx         | DSP version number                          |  |  |

| VKxxxx         | Conference DSP version number               |  |  |

| U(msg)         | undefined or unparseable message            |  |  |

• 5-12 •

Communicating with the PC

this page intentionally left blank

# 6.0 The H.100 Bus, Clock Modes & MC3 Bus

The Infinity Series H.100 MC3 Multi-Chassis Interconnect and Conference Board provides a means of connecting the fiber-optic MC3 interchassis bus to the H.100 bus. Through this bus, the MC3 channels can be connected to other H.100 compatible boards. The H.100 MC3/Conference Board also has facilities for conferencing and an analog port for music on hold or monitoring. It is capable of operating in a variety of clock modes compatible with H.100 and MC3 operation. In addition, the board is capable of interoperating with legacy MVIP and SCbus boards.

# 6.1 The H.100 Bus

The H.100 bus consists of 32 Pulse Code Modulation (PCM) streams operating at an 8.192 MHZ. clock rate. Each stream contains 128 timeslots, for a total of 4096 timeslots. In addition to the PCM data signals, there are a number of bit, frame, and network reference signals that are used to synchronize the operation of multiple boards. For interoperation with the legacy SCbus, MVIP-90 bus and the H-MVIP bus there are some additional clock signals that are included on the bus.

For the purposes of commands, a particular H.100 timeslot is referred to by a four digit hexadecimal number. The first two digits are the stream number, while the last two digits are the timeslot within the stream. Streams range from 00h to 1Fh, and timeslots from 00-7Fh.

The physical H.100 bus is a 68 conductor ribbon cable that connects the various boards in the system. As in any such bus, termination is important for its proper operation. The board at each end of the H.100 cable must have the proper termination installed or enabled, while any board between the ends must not terminate the bus. For the H.100 MC3/Conference

Board, termination is enabled using a command of the form **STab** where a controls the H.100 termination and b the MVIP bus termination. Termination is enabled if a is "E" and disabled if a is "D".

# 6.1.1 Legacy Bus Compatibility

The H.100 specification provides for inter-operability with several common legacy PCM busses. These include the SCbus, the MVIP-90 bus and the H-MVIP bus. Because these busses run at different bit rates than the 8.192 MHZ. of the H.100 bus, provisions exist in the specification to run the first 16 streams at either 4.096 MHZ. or 2.048 MHZ. For inter-operability with the SCbus, these streams typically should be run at 4.096 MHZ. (2.048 MHZ. and 8.192 MHZ are also possible choices) and with the MVIP-90 bus they should be run at 2.048 MHZ. H-MVIP runs these streams at either 2.048 or 8.192 MHZ. depending on whether MVIP-90 compatability is desired.

On the H.100 MC3/Conference Board, the bit rate of the first 16 streams is set using the "SB" command. This command takes the form **SBabcd** where the parameters a, b, c, and d select the bit rate for streams 0-3, 4-7, 8-11, and 12-15 respectively. The choices for these parameters are:

0 - 2.048 MHZ. 1 - 4.096 MHZ 2 - 8.192 MHZ.

Thus to operate with the SCbus at 4.096 MHZ. the command would be **SB1111** and to operate with the MVIP-90 bus **SB0000**. The default selection for these streams is the H.100 rate of 8.192 MHZ.

When operating in a compatability mode, the timeslot in board commands range from 00 to the maximum number of timeslots allowed by the bit rate. At 2.048 MHZ. timeslots within a stream are numbered 00-1Fh and at 4.096 the timeslots are 00-3Fh. MVIP-90 bus streams are numbered 00-0Fh. This numbering corresponds to the DSo/DSi convention according to the following table:

The H.100 MC3/Conference Board

• 6-2 •

| H.100<br>stream | MVIP-90<br>stream | MVIP-95<br>stream | H.100<br>stream | MVIP-90<br>stream | MVIP-95<br>stream |

|-----------------|-------------------|-------------------|-----------------|-------------------|-------------------|

| 00h             | DSo0              | HDS0              | 08h             | DSo4              | HDS8              |

| 01h             | DSi0              | HDS1              | 09h             | DSi4              | HDS9              |

| 02h             | DSo1              | HDS2              | 0Ah             | DSo5              | HDS10             |

| 03h             | DSi1              | HDS3              | 0Bh             | DSi5              | HDS11             |

| 04h             | DSo2              | HDS4              | 0Ch             | DSo6              | HDS12             |

| 05h             | DSi2              | HDS5              | 0Dh             | DSi6              | HDS13             |

| 06h             | DSo3              | HDS6              | 0Eh             | DSo7              | HDS14             |

| 07h             | DSi3              | HDS7              | 0Fh             | DSi7              | HDS15             |

# 6.2 Clock Modes

The H.100 bus specification defines a variety of clock signals. Two clock signals CT bus A and CT bus B are provided for redundancy. In addition, a signal called CT\_NETREF is defined which may be referenced to an external clock source such as a T1 or E1 span. This signal exists to aid in recovery if the primary clock source should fail. The specification also includes clock signals for compatibility with both the MVIP90 and SCbus.

The clock mode must be set before any connections can be made with other boards. The clock mode is set using the Set Clock command "SCmsabbc", where m is the clock mode, s is the sub-mode, and a, bb, and c are additional arguments used to select clock sources and specify compatibility modes. The default clock mode on a power up is to provide a local clock, but to neither source clock signals to the bus or derive the clock from the bus. The possible clock modes are:

- 0 no clocks to or from the bus

- 1 clocks slaved to the CT bus

- 2 the board is master CT bus clock A

- 3 the board is master CT bus clock B

- 4 the board is secondary master for CT bus clock A

- 5 the board is secondary master for CT bus clock B

Connections are possible only when all boards within a system are synchronized to the same clock. Only one board in a system can provide the H.100 bus clock. The other boards in the system must slave their internal clocks to the master. If the H.100 MC3/Conference Board is to use the H.100 bus clock, this clock must be provided by another board before switching can be accomplished.

## 6.2.1 Slave Mode

In the Slave Mode, the H.100 MC3/Conference board derives its clocks from one of the clock signals on the CT bus. The clock signal is selected with the submode argument in the **SC** command. The possible clock signals are:

- 0 CT bus clock A

- 1 CT bus clock B

- 2 SCbus clock at 2 MHZ.

- 3 SCbus clock at 4 MHZ.

- 4 SCbus clock at 8 MHZ.

- 5 MVIP90 clock signal

- 6 CT bus clock A, auto-fallback mode

- 7 CT bus clock B, auto-fallback mode

Argument a is used to set the CT\_NETREF mode, while argument bb is used to select the source of CT\_NETREF. The choices for argument a are:

0 - No CT\_NETREF output

- 1 CT\_NETREF\_1 output is enabled

- 2 CT\_NETREF\_2 output is enabled

It should be noted that CT\_NETREF\_2 is defined only for the H.110 bus and not the H.100 bus. It is included for upward compatibility. The

The H.100 MC3/Conference Board

• 6-4 •

### **6.2.2 Primary Master Mode**

In modes 2 or 3, the board supplies the CT master clocks A or B respectively. Other boards on the H.100 bus will synchronize to one of these clocks. The source of the clock is selected by the submode argument s. The choices are:

- 0 freerun, the board's internal clock

- 1 CT\_NETREF\_1

- 2 CT\_NETREF\_2 (not present on the H.100 bus)

- 3 a local network, either Ring 0 or Ring 1

- 4 a local network, either Ring 0 or Ring 1 with auto-fallback to CT\_NETREF

For submode 1 and 2, argument bb will select the frequency of the CT\_NETREF signal. The choices are:

00 - 8 kHz. (frame rate)

- 01 1.536 MHZ. (T1 rate)

- 02 1.544 MHZ. (T1 extended superframe rate)

- 03 2.048 MHZ. (E1 rate)

For submodes 3 and 4, argument bb will select either the MC3 Ring 0 if 00 or Ring 1 if 01. For submode 4, the optional argument c will specify the frequency of CT\_NETREF.

For all modes, argument a will select the legacy bus compatible clocks that the board will supply. The options are:

- 0 no compatibility clocks

- 1 SCbus clocks at 2 MHZ.

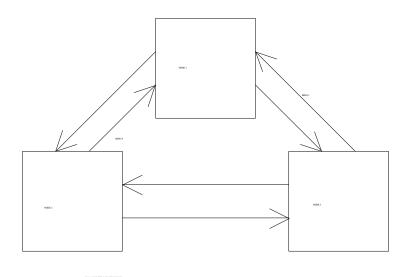

- 2 SCbus clocks at 4 MHZ.